Design space of Hafnia-FeCap-based 6T2C-nvSRAM

Power consumption has become a significant challenge for embedded edge devices, as their applications towards the Internet of Things are limited by the capacity of battery powers or energy harvesting systems. Despite performing operations at low activity frequencies, the volatile nature of SRAM results in leakage currents dominating the overall energy consumption. One of the prevalent solutions involves integrating non-volatile modules into a volatile SRAM cell, thereby creating a non-volatile SRAM (nvSRAM). Existing nvSRAM architectures typically rely on the employment of phase change memory (PCM), resistive random access memory (RRAM), or magnetic tunnel junction (MTJ), which usually require (1) additional transistors to suppress DC-short current of the non-volatile elements, (2) complex peripheral circuits and operation schemes to back up and recover the data bits regarding the memory properties, or (3) high dynamic power to operate the non-volatile units. Such scenarios can significantly increase the circuit complexity and energy consumption.

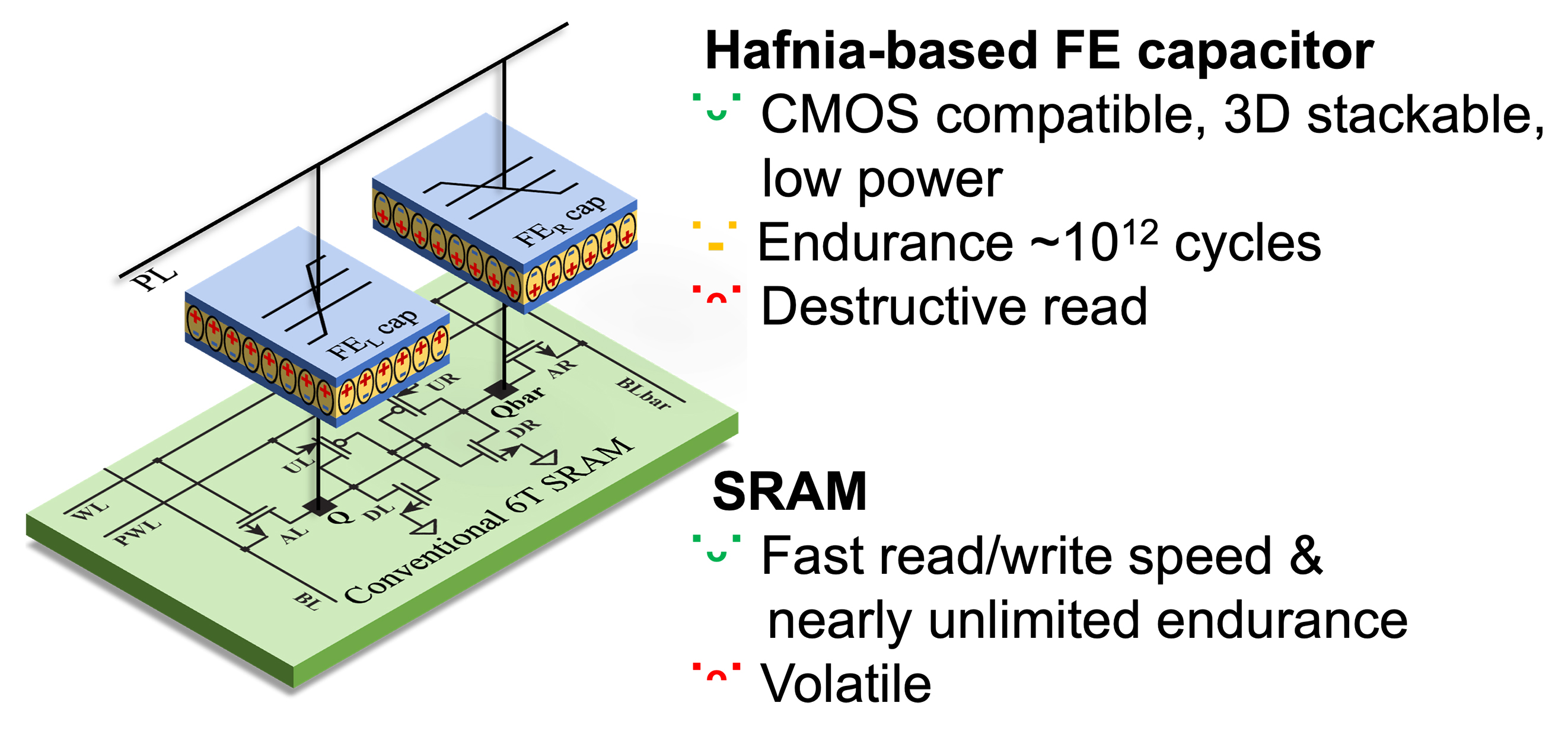

Polarization switching in ferroelectric materials has been widely studied and adopted for various types of memory technologies decades ago. However, the traditional perovskite-based ferroelectrics suffered from significant issues in their CMOS compatibility and physical thickness scalability. The recent discovery of ferroelectricity in CMOS-compatible HfO2-based thin films triggered a new wave of research interest in ferroelectric memory devices, demonstrating the great potential for their integration with advanced technology nodes and mass production. To date, different nvSRAM structures with HfO2-based ferroelectric capacitors (FeCaps) and ferroelectric field-effect transistors (FeFETs) have been proposed and investigated, aiming at mitigating the above challenges faced by previous nvSRAM designs utilizing other emerging memory devices. Among them, the 6T2C nvSRAM cell, implemented by simply stacking a pair of FeCaps onto the 6T-SRAM portion, shows the simplest structure, requires the fewest extra fabrication steps, and hence, becomes one of the most intriguing options in terms of density and cost. Additionally, the more robust endurance and retention of the FeCaps, when compared with the FeFET, can ensure a longer nvSRAM lifetime for frequent data updating and storing. However, previous proof-of-concept work has only experimentally demonstrated the functionalities of the 6T2C nvSRAM based on HfO2 FeCaps. Thorough evaluations of this type of devices, including their working principles and performance optimization, still await elucidation, which is critical for the further advancement of nvSRAM technologies.

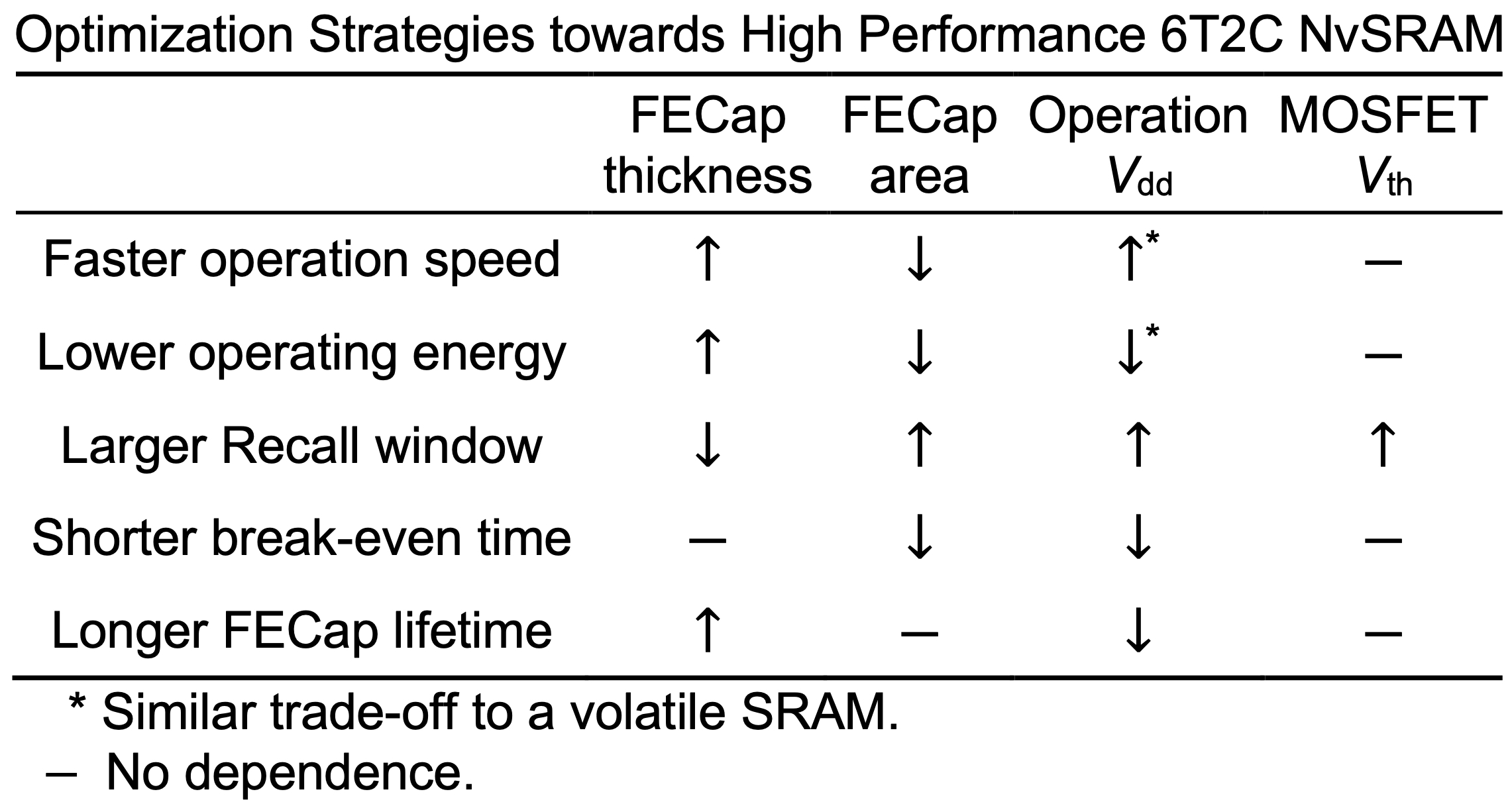

In this work, we first develop a device model for Hafnia-FeCap-based 6T2C nvSRAMs. By presenting the interplay between transistor and FeCap properties, we comprehensively evaluate the working principle of each operation mode within single 6T2C cells. We propose optimization strategies aimed at achieving robust and energy-efficient Recall/Store operations. Meanwhile, potential side effects on conventional SRAM operation modes that can arise from the introduction of FeCaps are also discussed. We also analyze the static power consumption and break-even time to assess the competitiveness of the approach against the sleep-mode strategy used in volatile SRAMs. The proposed strategies towards performance optimization are summarize below:

Yu Li, Keji Zhou, Hao Jiang*, Zhangcheng Huang, Xumeng Zhang, Yingfen Wei*, and Qi Liu

IEEE Transactions on Electron Devices, 2024.