Duty-cycle induced degradation problem in Hafnia-based ferroelectric devices

Ferroelectric Random-Access Memory (FeRAM) based on HfxZr1-xO2 materials has garnered widespread attention due to its high speed, excellent scalability, and compatibility with CMOS processes. However, the reliability of these devices is a key issue affecting their large-scale application. In read-intensive applications such as storage and artificial intelligence (AI), ferroelectric capacitors are neither frequently rewritten (as in traditional endurance tests), nor maintained in the same polarization state for a long period (as in traditional retention tests). Therefore, the reliability degradation and underlying physical mechanisms of devices in these application scenarios necessitates in-depth research.

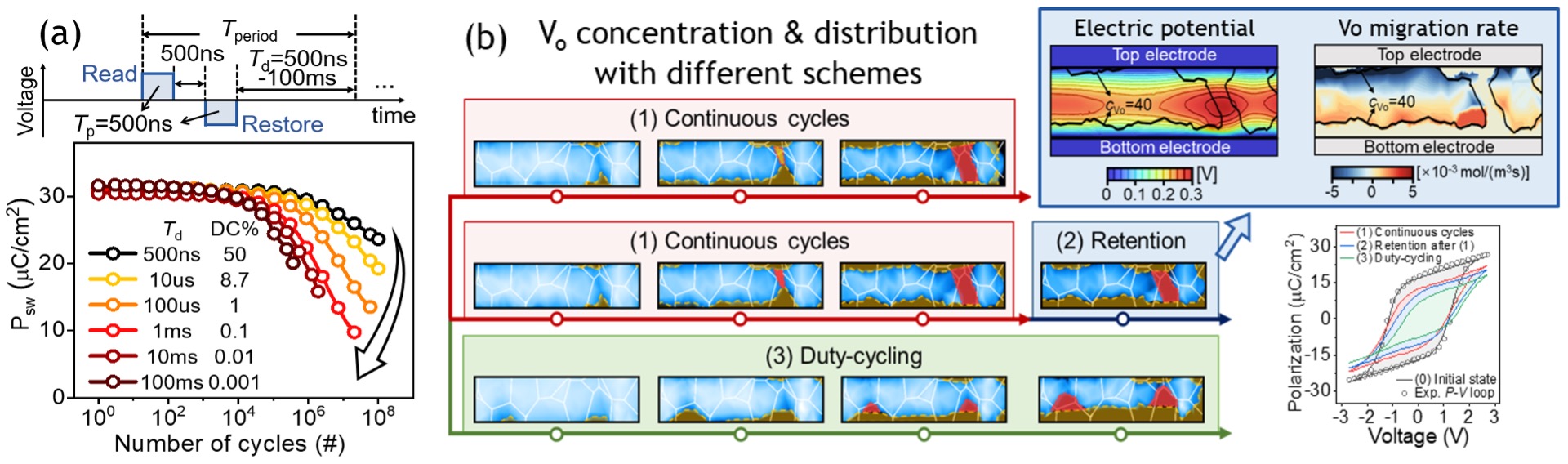

Addressing these issues, we proposed a duty cycling endurance test method, involving different pulse duty ratios. The study found that during electrical testing, as the duty cycle decreases, the loss of polarization intensity (Psw) and the shift in the switching voltage (Vc) become more pronounced, leading to faster device failure. Accordingly, we developed a three-dimensional physical model of ferroelectric devices incorporating the dynamics of oxygen vacancy defects and the Preisach polarization switching mechanism, revealing the failure mechanism driven by the redistribution of oxygen vacancies under the influence of electric fields and concentration gradients during duty cycling. Finally, we proposed the use of superlattice structures and the adjustment of Hf:Zr ratios to suppress the generation of oxygen vacancies under electrical stimuli, successfully mitigating the aforementioned failure behavior. This approach was validated on a 128 Kb Hafnia-based FeRAM chip, promoting broader applications of Hafnia-based ferroelectric memory technology.

Reference

Comprehensive Analysis of Duty-cycle Induced Degradations in HfxZr1-xO2-based Ferroelectric Capacitors: Behavior, Modeling, and Optimization

Guan Feng#, Yu Li#, Hao Jiang*, Xiaodong Wang, Yize Sun, Yingfen Wei*, Qi Liu, and Ming Liu

IEEE Symposium on VLSI Technology & Circuits, 2024.

#Equal contribution